Agilent E8045A

Analysis Probe System

for the Intel®

Pentium® 4 Processor

in the 478-Pin Package

**User's Guide**

# **Notices**

© Agilent Technologies, Inc. 2003

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Manual Part Number**

E8046-97000

#### **Print History**

E8046-97000, February 2003

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

### **Trademark Acknowledgements**

UNIX is a registered trademark of the Open Group.

Windows and MS Windows are U.S. registered trademarks of Microsoft Corporation.

Windows NT is a U.S. registered trademark of Microsoft Corporation.

### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

## **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

# **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license

terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

## **Safety Notices**

## **CAUTION**

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

## WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# **Contents**

| 1 | Equipment and Requirements                                                                        |

|---|---------------------------------------------------------------------------------------------------|

|   | In This Book 9                                                                                    |

|   | Equipment Supplied 10                                                                             |

|   | Additional equipment and software required 12                                                     |

|   | Overview of Installation and Setup 13                                                             |

|   | Additional Information Sources 15                                                                 |

| 2 | Preparing the Target System                                                                       |

|   | Mechanical Requirements 18                                                                        |

|   | Keep-Out Area On the Target Board 18                                                              |

|   | Figure 1. Keep-out area: interposer shadow as viewed from motherboard to bottom of interposer. 18 |

|   | Figure 2. Maximum component heights for Figure 1 19                                               |

|   | Table 1. Dimensions for keep-out volumes marked with alpha characters 19                          |

|   | Interposer Dimensions 20                                                                          |

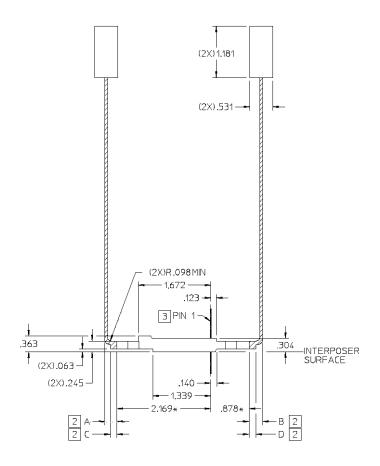

|   | Figure 3. Interposer dimensions 20                                                                |

|   | Socket 21                                                                                         |

|   | Clearance above the Target Board 21                                                               |

|   | Heatsink Requirements 22                                                                          |

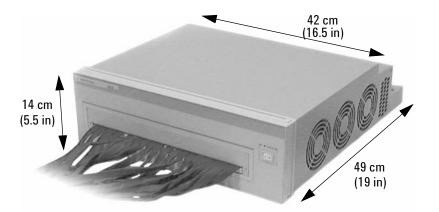

|   | Bench Space for the Analysis Probe 23                                                             |

|   | Figure 4. Analysis probe dimensions (approximate) 23                                              |

| 3 | Probing the Target System                                                                         |

|   | Desktop 26                                                                                        |

|   | Mobile Chip Cooler 26                                                                             |

Installing the Interposer with a

Desktop Retention Mechanism 28

Installing the Interposer with the

Mobile Chip Cooler Retention Mechanism 40

Uninstalling the analysis probe 48

To straighten bent pins 49

If a pin on the interposer breaks 49

### 4 Setting Up the Logic Analysis System

Power-ON/Power-OFF Sequence 52 52 To power-ON To power-OFF 52 To cycle power on the target system 52 Installing Logic Analyzer Modules **Installing Software** Installing and loading 55 What needs to be installed 55 To install software from floppy disk 56

# 5 Configuring the Logic Analysis System

**Loading Configuration Files**

To load configuration files 60 61 To create your own configuration files Deskewing the logic analyzer 62 When to deskew the analyzer To prepare to deskew To start the Probe Control Tool 63 To begin the deskewing process 64 66 To save settings and Eye Finder data To save Probe Control Tool settings 66

60

| To save Eye Finder data 66                      |

|-------------------------------------------------|

| To load Eye Finder data 67                      |

| Loading Symbol Information 68                   |

| To view predefined symbols 68                   |

| To load object file symbols 68                  |

| To access the Symbol Selector dialog 69         |

| To compensate for relocated code 70             |

| Setting Up Labels for Groups of Signals 71      |

| Predefined Label Descriptions 71                |

| To define additional labels 71                  |

| Configuring Signal Thresholds 72                |

| Capturing Execution                             |

| State and Timing Modes 74                       |

| Choosing Which States to Store 74               |

| To store all states 75                          |

| To store all except idle states 75              |

| To store all except idle and inactive states 76 |

| To use timing mode (Pass-Thru mode) 76          |

#### **Displaying Captured States** 7

Understanding the workspace 81 Data labels 81 To display the captured data 81 To display symbols 82

77 When to use the Trigger Mode tab

When to use the Sampling tab

Triggering on a transaction type

Setting Up Logic Analyzer Triggers To set up logic analyzer triggers 77

77

78

78

79

Other modes

6

| Displaying Signals as Waveforms 83  To display timing information 83                                                                                                                                                                                                                                                                           |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Using Dynamic Data Inversion 84  To use dynamic data inversion on the data bus  To disable dynamic data inversion 84                                                                                                                                                                                                                           | 84  |

| Using Other Tools to Process and Display Your Data Useful tools 85                                                                                                                                                                                                                                                                             | 85  |

| Troubleshooting the Analysis Probe                                                                                                                                                                                                                                                                                                             |     |

| Logic Analyzer Problems 88  Intermittent data errors 88  Unwanted triggers 88  Trigger not seen 89  No activity on activity indicators 89  No trace list display 89  Analysis Probe Problems 90  Target system will not boot up 90  Erratic trace measurements 91  Capacitive loading 91  Data bus is missing 91  Analysis probe shuts down 92 |     |

| Intermodule Measurement Problems 93                                                                                                                                                                                                                                                                                                            | 0.0 |

| An event wasn't captured by one of the modules                                                                                                                                                                                                                                                                                                 | 93  |

| Analysis Probe Messages 94  "Measurement Initialization Error" 94  "No Configuration File Loaded" 94  "Selected File is Incompatible" 94                                                                                                                                                                                                       |     |

"Slow or Missing Clock"

"Waiting for Trigger" 95

8

#### 9 Hardware Reference

98 Analysis probe—operating characteristics Table 2. Operating Characteristics 98 Table 3. Inputs and Outputs Table 4. Electrical Characteristics 99 Table 5. Environmental Characteristics (Operating) 100 Signal-to-connector mapping 101 Key 101 Data signals 102 Address Signals 106 109 **Control Signals General-Purpose ASCII (GPA) Symbol File Format GPA Record Format Summary** 115 SECTIONS 116 **FUNCTIONS** 117 **VARIABLES** 117 SOURCE LINES 118 START ADDRESS 119 Comments 119

#### 11 Service Guide

10

To return a part to Agilent Technologies for service 122

To get replacement parts 123

## 12 Safety Notices

Warnings 125

To clean the instrument 126

Safety Symbols 127

## **DECLARATION OF CONFORMITY**

Glossary

Index

# **Equipment and Requirements**

This chapter lists the equipment which is included with your analysis probe, and the additional equipment you need to make measurements.

## In This Book

This book documents the following products:

- Agilent E8045A Analysis Probe for the Intel® Pentium® 4 Processor in the 478-Pin Package

- Agilent E8046A Interposer

- Software and Accessories

# **Equipment Supplied**

This section lists equipment supplied with the analysis probe and equipment requirements for using the analysis probe.

The equipment supplied with the analysis probe is listed below:

- E8045A analysis probe (often called a "logic analyzer interface" or LAI).

- Analysis probe cables, attached to the analysis probe.

- E8046A interposer.

- Pin protector. Leave this pin protector in place until you plug the interposer into the target system.

- Retention module frame to support the heatsink when the interposer is in place.

- Parts kit for attaching the retention module frame and heatsink, including nuts, washers, screws, and a hex key. The kit also includes nylon hex screws and nuts for securing the analysis probe cables to the interposer. For your convenience, the kit contains extra quantities of some easy-to-misplace items.

- Cable ties, to help manage the analysis probe cables.

- Logic analyzer configuration files, and software on floppy disks or a CD-ROM.

- This *User's Guide*.

- Power cord for the analysis probe.

If the cord you received is not appropriate for your electrical power outlet type, contact your Agilent Technologies sales and service office. Use only the power cord supplied with the analysis probe.

See "To get replacement parts" on page 123 for a list part numbers.

## **1 Equipment and Requirements**

# Additional equipment and software required

In addition to the items supplied with the analysis probe, you need all of the following items:

- An Agilent 16700-series logic analysis system. You may need to upgrade the operating system (see page 55) so that it has the same version number as the configuration files.

- Five Agilent 16753/4/5/6A logic analyzer modules

- A small, flat blade screwdriver (used to open and close the ZIF socket). If your system uses a mobile socket, the blade of the screw driver must be no wider than 0.16 inches (4 mm).

# **Overview of Installation and Setup**

## CAUTION

Read the instructions in this manual and in the online help before using the Probe Control tool. For example, using the Debug Tab of the Probe Control tool may cause loss of data or equipment damage.

# NOTE

Be sure to read all of the installation instructions, with special attention to the precautions required to prevent equipment damage. Note that this manual also contains instructions for disconnecting the equipment.

- 1 Check that you received all of the necessary equipment. See "Equipment and Requirements" on page 9

- **2** Prepare the target system and the space around the target system. See "Preparing the Target System" on page 17

- 3 Install logic analyzer modules in your logic analysis system, if necessary. See "Installing Logic Analyzer Modules" on page 53

- **4** Make the physical connections. This includes:

- installing the interposer between the microprocessor and the socket on the target system,

- connecting the analysis probe cables to the interposer, and

- connecting the cables from the logic analyzer to the analysis probe.

See the "Probing the Target System" chapter.

- **5** Turn on the logic analysis system.

- **6** Install the software. See "Installing Software" on page 55.

#### **1 Equipment and Requirements**

- **7** Turn on the analysis probe, then the target system. See "Power-ON/Power-OFF Sequence" on page 52

- **8** Load a configuration file. See "Loading Configuration Files" on page 60

- **9** Deskew the analyzer using the Probe Control tool. See "Deskewing the logic analyzer" on page 62.

- 10 Begin making measurements.

# **Additional Information Sources**

Additional or updated information can be found in the following places:

- The **online help** for the Probe Control Tool has information on deskewing and configuring the analysis probe. The help includes information about using the Probe Control Tool which does not appear in this manual.

- The Installation Guide for the interposer contains instructions which are the same as those which appear in the "Probing the Target System" chapter of this manual.

- Newer editions of this manual may be available. Contact your local Agilent representative.

- The **measurement examples** include valuable tips for making analysis measurements. You can find the measurement examples under the system help in your 16700-series logic analysis system.

- Your Agilent representative may have additional background information which can help you solve your test and measurement problems.

**1 Equipment and Requirements**

2

# **Preparing the Target System**

This chapter describes the factors you need to consider when designing and preparing the target system for logic analysis with the analysis probe.

# **Mechanical Requirements**

# **Keep-Out Area On the Target Board**

The interposer extends slightly beyond the area normally occupied by the microprocessor. It is important to keep components from interfering with the interposer in this restricted area.

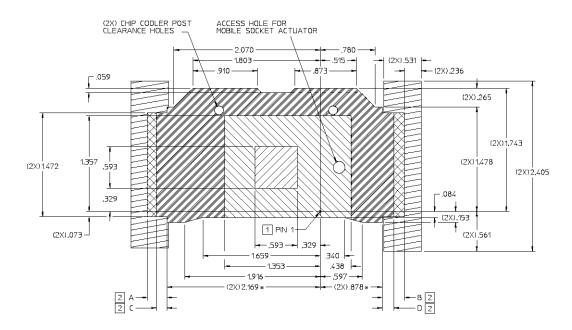

**Figure 1** Keep-out area: interposer shadow as viewed from mother-board to bottom of interposer.

Figure 1 depicts the shadow that the interposer would cast on the target motherboard. The hatched regions indicate the maximum allowable height of components located on the socket side of the motherboard.

#### Notes:

- \* Dimension indicates the edge of the rigid portion of the interposer.

- **1,3** Reference is center of A1 pin recess in the socket, in the locked position.

- **2** Because the flexible portion of the interposer is routed under the heatsink retention hardware, the keep-out volume changes for those dimensions with alpha characters.

**Table 1** Dimensions for keep-out volumes marked with alpha characters

| Platform                | Α     | В     | C     | C     |

|-------------------------|-------|-------|-------|-------|

| Desktop                 | 0.406 | 0.449 | 0.150 | 0.161 |

| Mobile with chip cooler | 0.161 | 0.161 | 0     | 0     |

Figure 2 Maximum component heights for Figure 1

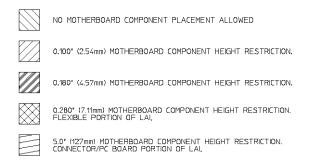

# **Interposer Dimensions**

The following illustration shows the approximate dimensions of the interposer. Design changes may result in slight variations from these dimensions.

Figure 3 Interposer dimensions

## **Socket**

The top of the socket must be flat. If the socket on your target system has ridges, they need to be removed.

# **Clearance above the Target Board**

Be careful to allow adequate space above the target board for the analysis probe, and for egress of the analysis probe cables.

The height of the paddles on the end of the interposer wings above the socket on the target system, without the analysis probe cables attached, is about 6.5 cm (about 3 inches).

# CAUTION

Allow enough room so that the interposer will not be twisted, pulled, or kinked during installation or use. See page 27 for a list of precautions to protect the interposer.

# **Heatsink Requirements**

The interposer is shipped with modified heatsink retention hardware which is designed to work specifically with the Intel-recommended heatsink.

If you use a heatsink of your own design, pay close attention to the keep-out area requirements on the previous page.

# **Bench Space for the Analysis Probe**

Take care to allow space for the analysis probe be placed near the target system and the logic analysis system. You will also need plenty of space near the analysis probe for the logic analysis system and expander frame.

Allow at least 5 cm clearance on both sides of the analysis probe for proper cooling.

CAUTION

Do not block the airflow holes on the sides of the analysis probe box. Blocked airflow may cause overheating and equipment damage

Figure 4 Analysis probe dimensions (approximate)

2 Preparing the Target System

# **Probing the Target System**

This chapter explains how to connect the Agilent E8046A interposer to the target system.  $\,$

CAUTION

To prevent equipment damage, remove power from the target system and analysis probe before making attachments.

NOTE

Installation requires access to the back of the motherboard.

This interposer can be installed using either of two general approaches, depending on the retention mechanisms. In either case, the goal is to raise the heat sink enough to allow room for the interposer.

# **Desktop**

Standoffs are added below the retention module brackets.

# **Mobile Chip Cooler**

Longer mounting pins are installed.

#### **Protecting the Interposer**

Here is a summary of precautions to take to avoid damaging the interposer:

DO minimize the removal of the analysis probe cables, once they are connected to the interposer.

DO minimize the removal of the interposer, once it is connected to the microprocessor and target system.

DO exercise patience and care when working with the interposer.

DO use ESD precautions.

DO remove power from the target system and analysis probe before making attachments.

DO protect the pins from damage by covering them with the pin protector when the interposer is not in use.

DO NOT insert any kind of tool between the interposer and the microprocessor, except as described in this manual.

DO NOT kink the analysis probe cables.

DO NOT pull on or twist the cables which are attached to the interposer.

# Installing the Interposer with a Desktop Retention Mechanism

- **1** Gather the required parts:

- E8046A interposer

From the accessory kit supplied with the interposer:

- 4 metal standoffs

- · 4 nylon washers

- 8 short metal screws

- Retention module frame

- 7/64 inch hex key

• Small flat blade screwdriver (you need to supply this)

2 Disconnect power from the fan.

$\boldsymbol{3}$   $\,$  Remove the heatsink and fan from the microprocessor.

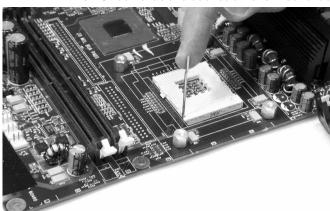

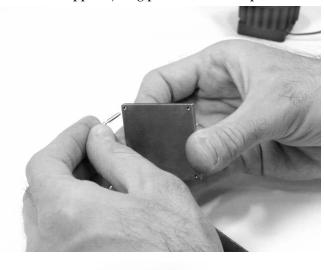

**4** Check that the socket on the interposer is open.

**6** Align the processor over the socket on the interposer. Gently align the the processor with the socket until you feel the pins fall into the holes. Visually check that the bottom of the processor is flush with the top of the socket on the interposer, then close the socket.

CAUTION

Note that the orientation of the processor with respect to the interposer socket is opposite from the target system. A dot on the interposer indicates the position of pin A1.

**7** Remove the retention module frame from the motherboard.

To remove the retention module and install the standoffs, you need to have access to the back side of the botherboard.

Put the fasteners and retention module aside in a safe place.

- **8** Install the standoffs on the motherboard.

- For desktop sockets, use the metal standoffs.

- For mobile sockets, use the nylon standoffs.

Use the supplied short metal screws and nylon washers, from the bottom side of the motherboard, to attach the standoffs.

**9** Check that the socket on the motherboard is open.

**10** Remove the pin protector from the interposer.

Keep the pin protector. You will need it to prevent damage to the interposer whenever the interposer is not plugged into the target system. The pin protector is an "off the shelf" mPGA478B socket.

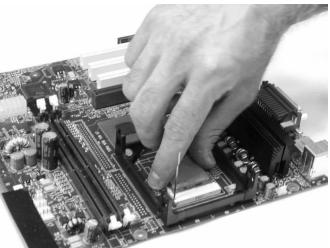

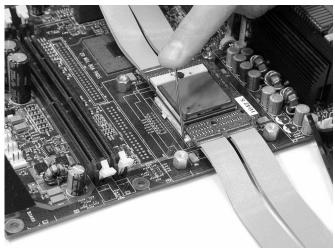

**11** Align the interposer over the socket on the target system.

Note how the socket on the interposer is rotated 180° relative to the socket on the target system.

Gently align the assembly until you feel the pins fall into the holes of the socket.

**12** Close the socket on the motherboard.

If necessary, use one hand to hold the interposer flat against the socket.

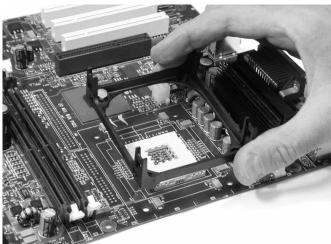

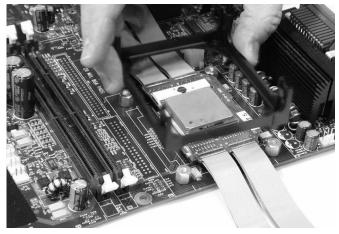

**13** Install the supplied retention module, using the supplied short screws to secure it to the top of the standoffs.

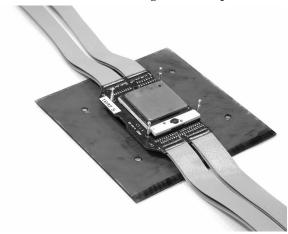

The interposer cables should pass under the retention module.

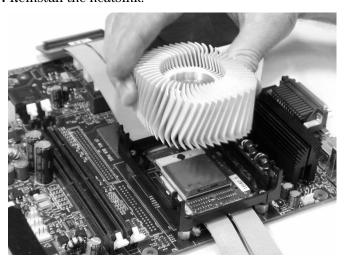

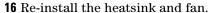

**14** Reinstall the heatsink.

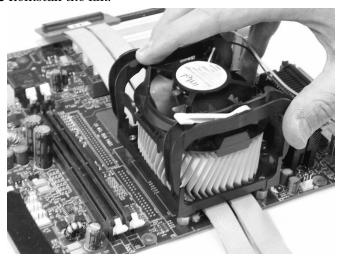

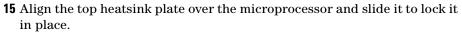

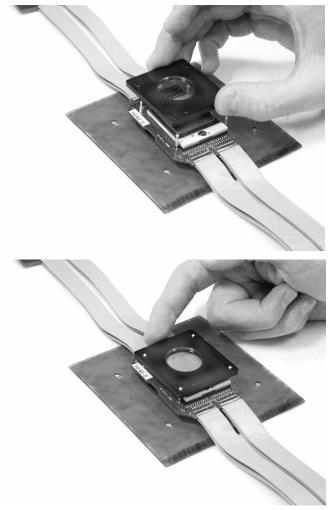

#### **15** Reinstall the fan.

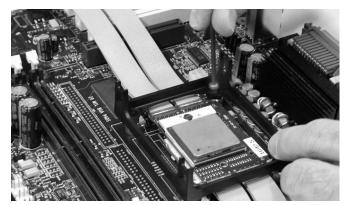

**16** Reconnect power to the fan.

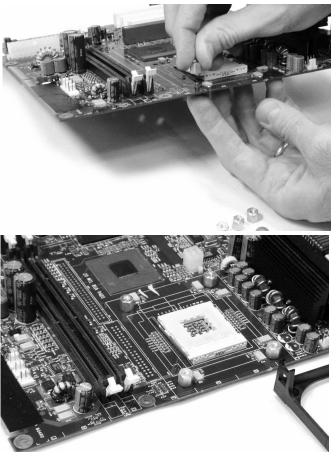

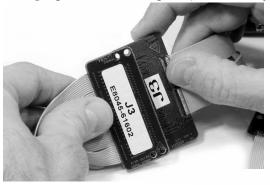

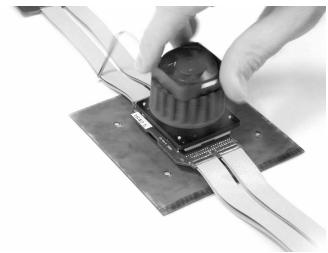

17 Connect the analysis probe cables to the interposer.

Refer to the labels on the interposer and on the cable paddles. Be careful to plug the cables straight in, without any rocking motion.

**18** Optional: install the supplied nylon screws to keep the paddles on the end of the analysis probe cables for additional retention.

**19** Connect the analysis probe to the logic analyzer.

Connect the pod cables to the connectors on the analysis probe as shown on the back of the analysis probe.

## Installing the Interposer with the Mobile Chip Cooler Retention Mechanism

- **1** Gather the required parts:

- E8046A interposer

4 extended pins from the accessory kit supplied with the interposer

- Small flat blade screwdriver (you need to supply this)

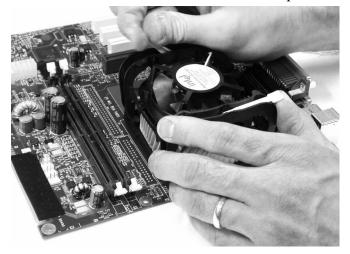

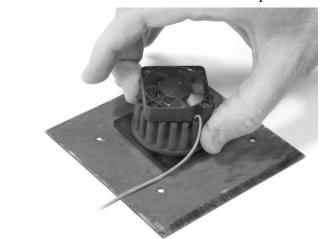

- **2** Remove the heatsink and fan from the microprocessor.

**3** Remove the bottom plate, with its 4 pins attached, from the back of the motherboard.

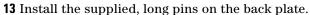

**4** Remove the 4 pins from the bottom plate.

Store the original pins in a safe place. The pins supplied with the interposer may be used with or without an interposer installed.

- **5** Check that the socket on the interposer is open.

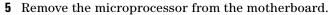

- **6** Remove the microprocessor from the motherboard.

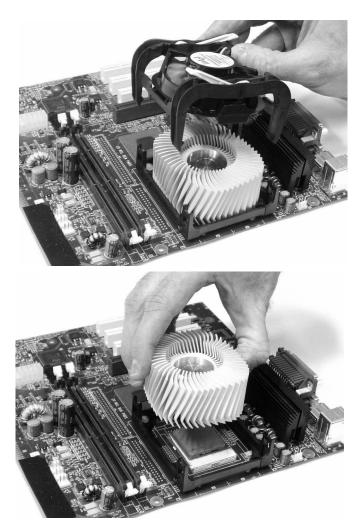

- 7 Align the processor over the socket on the interposer. Gently align the the processor with the socket until you feel the pins fall into the holes. Visually check that the bottom of the processor is flush with the top of the socket on the interposer, then close the socket.

CAUTION

Note that the orientation of the processor with respect to the interposer socket is opposite from the target system. A dot on the interposer indicates the position of pin A1.

**8** Check that the socket on the target system is open.

**9** Remove the pin protector from the interposer.

Keep the pin protector. You will need it to prevent damage to the interposer whenever the interposer is not plugged into the target system. The pin protector is an "off the shelf" mPGA478B socket.

**10** Align the interposer over the socket on the target system.

You may need to bend the cables of the interposer upward.

Note how the socket on the interposer is rotated  $180\,^\circ$  relative to the socket on the target system.

**11** Gently align the assembly until you feel the pins fall into the holes of the socket on the motherboard.

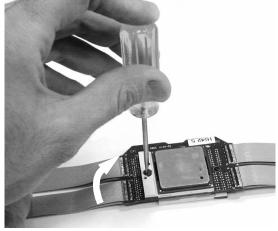

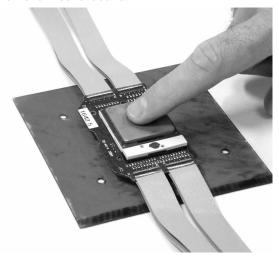

**12** Close the the socket on the target system.

Insert a narrow, flat blade screw driver through the hole in the interposer.

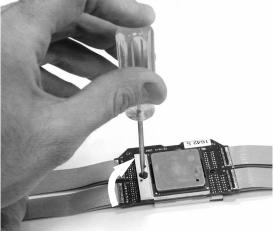

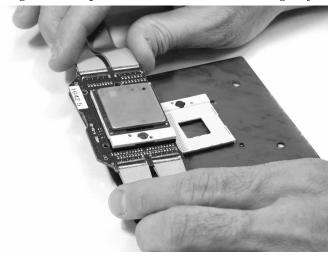

**14** Install the back plate. The pins should pass through the back of the motherboard and through the interposer.

Tip: Rotate the top portion of the heatsink counterclockwise before installing it, then re-tighten the heatsink once it's on the interposer.

17 Connect the analysis probe cables to the interposer.

Refer to the labels on the interposer and on the cable paddles. Be careful to plug the cables straight in, without any rocking motion.

**18** Optional: install the supplied nylon screws to keep the paddles on the end of the analysis probe cables for additional retention.

**19** Connect the analysis probe to the logic analyzer.

Connect the pod cables to the connectors on the analysis probe as shown on the back of the analysis probe.

## Uninstalling the analysis probe

CAUTION

To maximize the life of the interposer and socket, minimize uninstalling and reinstalling the interposer.

CAUTION

If possible, leave the analysis probe cables attached to the interposer.

CAUTION

Use ESD precautions. Electrostatic discharge (ESD) can damage the interposer, as well as the target system. Use grounded wrist straps and mats when you handle the interposer.

- **1** Remove power from the target system and from the analysis probe.

- You may leave the logic analysis system turned on.

- **2** Remove the heatsink.

- **3** Remove the processor from the interposer.

- **4** Remove the interposer from the target system.

- **5** Remove the retention module frame.

- **6** Re-install the processor on the target system.

- **7** Re-install the heatsink.

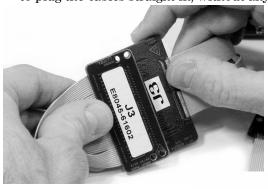

## To straighten bent pins

When handling or installing the processor or the interposer, care must be taken not to bend pins. Here is a practical suggestion for straightening bent pins:

- 1 Find a 0.5mm mechanical pencil.

- **2** Remove the lead from the tip of the pencil.

- **3** Place the tip of the pencil over the bent pin and bend it to the correct angle.

#### If a pin on the interposer breaks

Broken pins cannot be repaired.

If only one pin (or a few pins) on the interposer is broken, check whether the pin carries a signal which you need to capture. If the pin is a ground or power pin, measurements should not be affected.

To find out whether the broken pin is an "important" one, consult your pinout documentation for the processor.

**3 Probing the Target System**

4

## **Setting Up the Logic Analysis System**

This chapter shows you how to power on the logic analysis system, how to set up the logic analyzer modules, and how to install the software.

## Power-ON/Power-OFF Sequence

Listed below are the sequences for powering on and off a fully connected system. Simply stated, your target system is always the last to be powered on, and the first to be powered off.

Use only the power cord supplied with the analysis probe.

#### To power-ON

Ensure the target system is powered off.

- **1** Turn on the logic analysis system.

- **2** Turn on the analysis probe.

- **3** Configure the logic analysis system. See "Configuring the Logic Analysis System" on page 59.

- **4** When the logic analysis system is connected to the target system, and everything is configured, turn on your target system.

#### To power-OFF

Turn off power to your system in the following order:

- 1 Turn off your target system.

- 2 Turn off the analysis probe.

- **3** Turn off your logic analysis system.

### To cycle power on the target system

• Cycle power on the target system only. You do not need to turn off the analysis probe or logic analysis system.

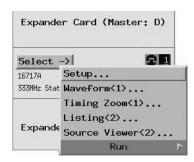

## **Installing Logic Analyzer Modules**

You should install logic analyzer modules in your logic analysis system before you begin make connections or configure the logic analysis system.

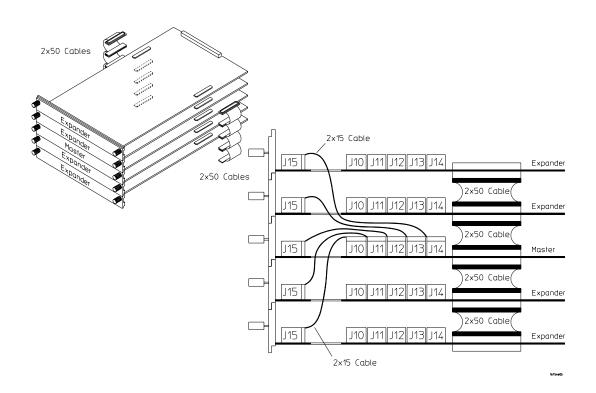

Five logic analyzer cards in the logic analysis system must be connected together as one machine. Connect the cards so that the master card is in slot C (or slot H in an expander frame).

Use five  $2 \times 15$  cables and eight  $2 \times 50$  cables (in the accessory pouch) to connect the modules

NOTE

Turn off the mainframe power before removing, replacing, or installing modules.

All of the cards machine should be of the same type.

Refer to the Agilent 16700-series logic analysis system's *Installation Guide* for more information on how to install the cards and connect them together.

## **Installing Software**

This section explains how to install the software you will need for your analysis probe.

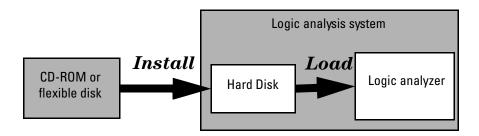

#### **Installing and loading**

Installing the software will copy the files to the hard disk of your logic analysis system. Later, you will need to load some of the files into the logic analyzer module.

#### What needs to be installed

Install the following software from the provided floppy disks or CD-ROMs:

- 1 Logic analysis system operating system patches, if applicable.

- **2** Logic analysis system configuration files.

NOTE

Install the disks in the order listed above.

The version number of the operating system must match the version number of the configuration files.

The logic analysis system will end the current session after installing the patch and again after installing the configuration files.

Installing the configuration files also installs the Probe Control tool software.

#### To install software from floppy disk

Installing a processor support package will take just a few minutes.

- 1 Insert the first disk in the drive.

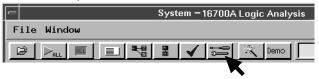

- 2 Select the System Admin icon.

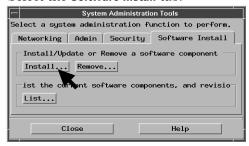

3 Select the **Software Install** tab.

4 Select Install....

Change the media type to "Floppy Disk" if necessary.

- 5 Select Apply.

- **6** Select the *E8045A Preprocessor* software package.

If you are installing from a floppy disk, only one package will be listed.

7 Select Install.

The Continue dialog box will appear.

#### 8 Select Continue.

The dialog box will display "Progress: completed successfully" when the installation is complete.

**9** If required, the system will automatically reboot. Otherwise, close the software installation windows.

The configuration files are stored in /logic/configs/hp/E8045A.

The inverse assembler is stored in /logic/ia.

See the on-line help for more information on installing, licensing, and removing software.

4 Setting Up the Logic Analysis System

# **5** Configuring the Logic Analysis System

This chapter shows you how to load configuration files, which set up the logic analysis system for your microprocessor, and how to further configure the software before you begin making measurements.

## **Loading Configuration Files**

The first step in configuring the logic analyzer is loading a configuration file. The information in the configuration file includes:

- · Label names and channel assignments for the logic analyzer.

- Settings for State or Timing modes.

There are two configuration files: one for the State modes and one for Timing mode.

#### To load configuration files

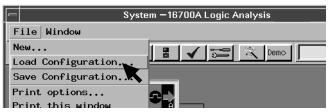

1 In the System window, select the Load Configuration... command from the File menu.

2 In the File Manager dialog, browse to the /logic/configs/hp/E8045A directory

If this directory does not exist, see "To install software from floppy disk" on page 56.

**3** Using File Manager, select the configuration file from the configuration file directory, then click load.

Load **E8045\_state.**\_\_\_ for state mode (synchronous measurements).

Load **E8045\_timing.**\_\_\_ for timing mode.

4 Close File Manager.

When you load a configuration file, the following things happen:

- The workspace is set up.

- The state (synchronous) or timing sampling mode is selected.

- Buses and signals coming from the analysis probe to logic analyzer channels are mapped to labels.

- Logic analyzer pod threshold voltages are set.

- If the configuration was originally saved "with data," then Eye Finder data is loaded.

#### NOTE

You must set up the sampling mode and analyzer labels by loading a system configuration file. Do not attempt to change between state and timing mode without loading the appropriate configuration, because the logic analyzer labels are different in these two modes.

The version number of the configuration file must match the version number of the logic analysis system's operating system.

#### To create your own configuration files

If you create and save your own configurations, start with a copy the supplied configuration file and delete the labels you don't need, rather than building a configuration from scratch.

There are some characteristics of the supplied configuration file that you should be aware of:

- The data bus is split between four labels. The upper and lower 32 bits are split (this is necessary because the logic analyzer allows only 32 bits to be assigned to a label). Quad pumped data is reduced to double pumped. P strobe data is labeled \_1 and N strobe data is labeled \_2.

- To save a configuration, be sure to save the whole workspace, not just the logic analyzer configuration.

See the online help in any logic analysis system window for general information on modifying, saving, and loading configuration files.

## **Deskewing the logic analyzer**

You must deskew the analyzer before running any state mode measurements. Deskewing trains the logic analyzer to sample each signal at the moment that it is most likely to be stable.

To deskew the analyzer, use the Probe Control tool. More information on deskewing can be found by selecting Help > On this window from the Probe Control tool.

#### When to deskew the analyzer

Deskew the analyzer when:

- Any of the logic analyzer modules in the logic analysis system are replaced.

- Changes are made to the analysis probe or to the logic analyzer modules.

- The temperature is changed significantly.

- The frequency of the front-side bus being probed is changed to a frequency which is higher than what was used to deskew the analyzer.

- The analyzer mode is changed between Timing and State. (Reminder: to change between Timing and State modes, you must load the appropriate configuration file.) If you have saved Eye Finder data for the analyzer mode, you may reload that data instead of deskewing again.

- The analysis probe is connected to a new target system.

#### To prepare to deskew

- 1 Make sure the analysis probe is connected to the interposer.

- **2** Make sure the interposer is connected to the target system.

- **3** Make sure the analysis probe is connected to the logic analysis system.

- **4** Make sure the analysis probe and target system are both turned on.

**5** Make sure the target system is in a mode where it is supplying the BCLK signal. If your target has the ability to generate BCLK at different frequencies, it is recommended that you use the highest frequency (up to 200 MHz) for deskewing.

#### To start the Probe Control Tool

- 1 Display the Workspace window.

- **2** Loading one of the provided configuration files places a Probe Control Tool on the workspace. If the tool was removed from the workspace, drag a Probe Control Tool onto the workspace.

- **3** Open the Probe Control Tool.

#### If a single analysis probe is connected

When you select the *Connect* tab, the source will be highlighted on the list and the *Select Source* button will already be selected.

#### If several analysis probes are connected

- 1 Select the Connect tab.

- **2** Select which analysis probe you want to set up using the Probe Control Tool.

3 Select Source.

#### If no analysis probes are displayed

If no analysis probes are displayed on the Connect tab:

- 1 Check that the analysis probe is physically connected to the logic analysis system.

- **2** Check that the analysis probe is powered on.

- **3** Run the target so that it is supplying BCLK. Go to the Format tab of the analyzer and look for activity on clk C[J]. Activity on this signal is a good indication that the logic analyzer cables and interposer cables *are* correctly connected. (Note that the opposite does not hold true: it is possible that BCLK will not be detected because the Probe Control tool has not yet set up the comparators in the analysis probe.)

- 4 Select Search Source.

The Probe Control tool does not need to be connected to any other tools in the workspace.

CAUTION

Read the instructions in this manual and in the online help before using other tabs of the Probe Control tool. For example, using the Debug Tab of the Probe Control tool may cause loss of data or equipment damage.

#### To begin the deskewing process

- 1 Make sure that a BCLK signal is being provided from the target system (see "To prepare to deskew" on page 62).

- **2** Open the Probe Control Tool.

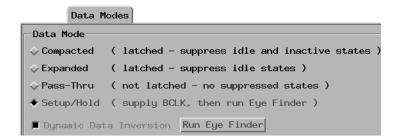

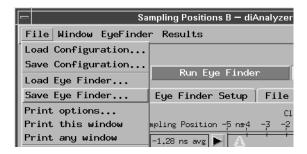

- **3** Select the *Data Modes* tab.

- **4** Select the *Setup/Hold* mode.

This step enables the Run Eye Finder button.

- **5** Select *Run Eye Finder*. It takes about 15-20 minutes to deskew the analyzer. Progress is displayed in the Eye Finder results window.

- **6** Save the Eye Finder data.

## To save settings and Eye Finder data

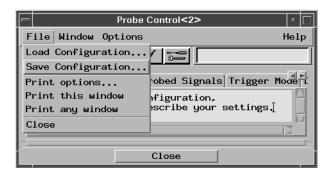

#### To save Probe Control Tool settings

- 1 (Optional) Enter a description of the current set-up in the Comments tab of the Probe Control Tool. It is often helpful to include information (such as serial numbers) which can uniquely identify the logic analyzer, analysis probe, interposer, and target system for which the configuration is valid.

- **2** Save a configuration, using the File menu of any tool in the workspace.

The configuration file will include any changes you have made from the supplied configuration file, including:

- Changes to the workspace.

- Changes to labels in logic analyzer machine or in any of the display tools.

- Changes to settings in the Probe Control Tool.

## To save Eye Finder data

• In the Eye Finder (that is, in the Sampling Positions dialog) use the File menu to save the results of the deskewing process.

Choose a file name which specifies the bus frequency and the analyzer setup.

It is a good idea to save Eye Finder data *immediately* after deskewing the analyzer and verifying the results.

#### To load Eye Finder data

Load Eye Finder data after you have loaded a new state configuration file.

#### NOTE

Each Eye Finder data file is specific to the logic analysis system setup which was used for the deskewing run. If the hardware setup has changed in any way (see "When to deskew the analyzer" on page 62) then you should deskew again.

- 1 Open the logic analyzer's Sampling tab.

- 2 Select Sampling Positions....

- **3** Select File then Load Eye Finder....

- **4** Select the file to load.

See "Deskewing the logic analyzer" on page 62 for more information on deskewing.

See the Help menu in the Sampling Positions dialog for more information about Eye Finder data files.

## **Loading Symbol Information**

Symbols are more easily recognized than hexadecimal address values in logic analyzer trace displays, and they are easier to remember when setting up triggers.

Agilent logic analyzers let you assign user-defined symbol names to particular label values.

Also, you can download symbols from certain object file formats into Agilent logic analyzers.

#### To view predefined symbols

User-defined symbols are symbols you create in the logic analyzer by assigning symbol names to label values. Typically, you assign symbol names to address label values, but you can define symbols for data, status, or other label values as well.

User-defined symbols are saved with logic analyzer configurations. The supplied logic analyzer configuration files contain predefined symbols for logic analyzer labels.

To display the predefined symbols:

- 1 Open the logic analyzer's Setup window.

- **2** Select the Symbols tab.

- **3** Select the User Defined Symbols tab.

- 4 Choose a label name from the "Label" list.

The logic analyzer will display the symbols associated with the label.

#### To load object file symbols

The most common way to load program symbols into the logic analyzer is from an object file that is created when the program is compiled. The object file containing symbolic debug information must be in a format the logic analyzer understands. If your compiler generates object files in a format that the logic analyzer doesn't understand, you can use a General-Purpose ASCII (GPA) symbol file (see "General-Purpose ASCII (GPA) Symbol File Format" on page 113).

To load symbols in the Agilent 16700-series logic analysis system:

- 1 Open the logic analyzer module's Setup window.

- **2** Click the Symbol tab.

- 3 Click the Object File tab.

Make sure the label is ADDR.

From this dialog you can select object files and load their symbol information.

When you load object file symbols into a logic analyzer, a database of symbol/line number to address assignments is generated from the object file.

## To access the Symbol Selector dialog

The Symbol Selector dialog allows you to view the database so you can find a symbol to use in place of a hexadecimal value when defining trigger patterns, trigger ranges, and so on.

The Symbol Selector dialog may be accessed in various ways. One way to access the Symbol Selector dialog is from the Search tab in the Listing display.

- 1 Under the Search tab in the Listing display, click Advanced Searching.

- 2 In the Goto Pattern dialog, click Define.

- 3 In the Search Pattern dialog, select the Symbols numeric base.

- **4** Select Pattern, Range, Not Pattern, or Not Range.

- **5** Click the field to the right of the Pattern/Range selection button.

- **6** In the Symbol Selector dialog that appears, select the symbol you want to use.

#### To compensate for relocated code

When code segments are relocated, or when memory management units produce fixed code offsets, you can compensate by using the address offset field in the Symbol Selector dialog.

Entering the appropriate address offset will cause the logic analyzer to reference the correct symbol information for the relocatable or offset code.

## **Setting Up Labels for Groups of Signals**

## **Predefined Label Descriptions**

The logic analyzer configuration file automatically sets up labels for most microprocessor signals.

Labels which correspond to processor signals are displayed in upper case.

Labels which for signals which are generated by the analysis probe are generally displayed in lower case.

For a list of all of the signals, see "Signal-to-connector mapping" on page 102.

#### To define additional labels

- 1 Open the Setup window.

- 2 Click the Format tab.

- 3 Click a label and select Insert before... or Insert after....

- **4** Click the signals under the appropriate pod, then select which bits to include in the label.

## **Configuring Signal Thresholds**

## CAUTION

#### Do not change the signal thresholds or set-up and hold times.

Remember that the logic analyzer is connected to the analysis probe. Changing these parameters will only disrupt the communication between the analysis probe and the logic analyzer—it will not affect how the analysis probe acquires signals from the processor.

# Capturing Execution

This chapter shows you how to set up logic analyzer triggers to capture just the data you want.

The normal steps in using the logic analyzer are:

- 1 Configure the logic analyzer.

- **2** Load symbols from the program's object file.

- **3** Set up the trigger, and run the measurement.

- 4 Display the captured data.

The logic analyzer is configured, and labels are created (formatted) for the logic analysis channels when configuration files are loaded (see "Loading Configuration Files" on page 60).

You can load program object file symbols into the logic analyzer when configuring it (see "Loading Configuration Files" on page 60).

This chapter describes setting up logic analyzer triggers. See "Displaying Captured States" on page 81 for information on displaying captured data.

NOTE

Note: The screens you see may be different from what you see in this manual, depending on the version of your logic analyzer system software.

# **State and Timing Modes**

You can capture data in state mode (where data is sampled sychronously with BCLK) or in timing mode (where data is sampled asynchronously and you can see the timing relationships between signals).

NOTE

You *must* set up the sampling mode and analyzer labels by loading a system configuration file. Do not attempt to change between state and timing mode without loading the appropriate configuration file (E8045\_timing.\_\_\_ or E8045\_state.\_\_\_), because the logic analyzer labels are different in these two modes.

NOTE

You *must* deskew the analyzer before capturing data in state mode. You can either use the Probe Control tool to deskew the analyzer, or load previously saved Eye Finder data. See "Deskewing the logic analyzer" on page 62.

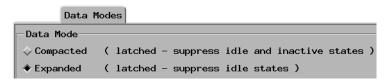

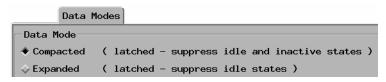

#### **Choosing Which States to Store**

In state mode, you can control how much data is captured by the analyzer, and make the listing display easier to read, by using storage qualification to store only selected kinds of states.

Storage qualification acts as a real-time filter which allow you to selectively remove idle states and snoop stalls from the captured data. For uses such as BIOS debug, removing idles and snoop stalls provide a more compact and readable view of the bus to optimize the capture of pertinent data in the trace memory of the analyzer.

Storage qualification can be set up using a combination of:

- The settings under the Data Mode tab, and

- The default storing configuration in the logic analyzer's Setup window.

#### To store all states

Also known as "All" mode.

- 1 Open the Probe Control Tool and select the Data Mode tab.

- **2** Select either Compacted or Expanded.

- **3** Open the Setup window.

- 4 Select the Trigger tab.

- **5** Select the Default Storing tab.

- **6** Set Store by default to Custom, and set storage qualification to "Anything".

## To store all except idle states

Also known as "Expanded" mode. This mode stores states whenever a bus cycle is active, the data bus is active, BINIT# is active a Reset is active, and two BCLK states after Reset.

- 1 Open the Probe Control Tool and select the Data Mode tab.

- 2 Select Expanded.

- **3** Open the Setup window.

- **4** Select the Trigger tab.

- **5** Select the Default Storing tab.

- **6** Set Store by default to Custom, and set storage qualification to "Store if Cqual# = 0".

#### To store all except idle and inactive states

Also known as "Compacted" mode. This mode stores the same states as Expanded mode, except for consecutive reset states, consecutive snoop stalls, and states where the data bus is active but no data is being transferred. This is the default mode.

- 1 Open the Probe Control Tool and select the Data Mode tab.

- **2** Select Compacted.

- **3** Open the Setup window.

- 4 Select the Trigger tab.

- **5** Select the Default Storing tab.

- **6** Set Store by default to Custom, and set storage qualification to "Store if Cqual# = 0".

## To use timing mode (Pass-Thru mode)

- 1 If you have already deskewed the analyzer, make sure that you have saved the Eye Finder data. If the Eye Finder data is not saved, you will need to deskew the analysis probe again when you go back to State mode.

- **2** Load the Timing configuration file (E8045\_timing.\_\_\_ or another system configuration file which you have saved based on this file).

NOTE

Do not try to enable timing mode just by selecting the Pass-Thru data mode. Instead, you must load a Timing configuration file, which will change the analyzer mode to Timing mode, change the analysis probe mode to Pass-Thru, and change the signal mappings.

#### Other modes

The Setup/Hold mode is used to deskew the analyzer.

See also "Dynamic Data Inversion" in the Probe Control tool online help.

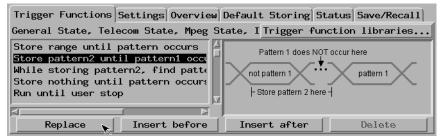

#### When to use the Trigger Mode tab

In most cases, you will not need to make any changes under this tab.

The Trigger Mode tab of the Probe Control tool lets you add additional data labels which can be used by logic analyzer triggers in state mode.

Always select Modified General State mode (this is the default).

The data labels (Dxx and DBIx) are selected by default. Do not delete them.

Add additional labels here if:

- You have defined a new label for some data signals, AND

- The new label does not use the same signals as any label set up by the configuration file, AND

- You want to use the new label in a trigger.

### When to use the Sampling tab

You may safely use the Sampling tab of the logic analyzer's Setup and Trigger window to change:

- Trigger position (start/center/end)

- Sampling positions (after deskewing, to "fine-tune" the results if necessary)

- Acquisition speed/depth

Many of the settings are set by the configuration files and should not be modified. *Do not* use the Sampling tab to change:

- Analyzer mode (state/timing/eye scan)

- Clock setup

# **Setting Up Logic Analyzer Triggers**

## To set up logic analyzer triggers

1 Open the logic analyzer's Setup window.

2 Select the Trigger tab.

**3** Select the trigger function that will be used in the logic analysis measurement and press the Replace button.

**4** Define the patterns, ranges, and other resources that will be used in the logic analysis measurement.

**5** Run the measurement.

Refer to the online help for the Probe Control tool for information about triggering on data labels which you have added.

Refer to the Agilent 16700-series logic analysis system's on-line help for general information on setting up logic analyzer triggers.

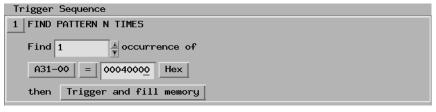

## Triggering on a transaction type

#### Triggering on address and transaction type

To trigger on a specific address and transaction type, use the A35-32, A31-00, and TranTy labels, together with the TranTy label symbols. The symbols identify each transaction type uniquely, except for Interrupt Acknowledge and Special Transactions, which are combined into one symbol.

#### Triggering on data and transaction type

There is no guaranteed method of triggering on a particular transaction type or address ANDed with a particular data value in a target system with overlapping transactions. Alignment in the Listing window is the result of post-processing and cannot be used for triggering. The analysis probe hardware captures this information on different states. A trigger specification could be defined to find a certain transaction type; however, by the time the data pattern is found, it could belong to a different transaction.

**6 Capturing Execution**

# **Displaying Captured States**

This chapter shows how to display, filter, and interpret data which has been captured by the logic analysis system.

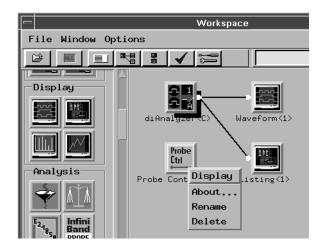

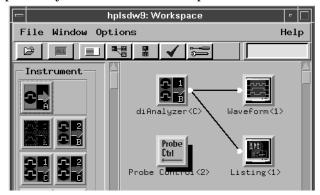

## **Understanding the workspace**

The Workspace window shows the relationship between the parts of your measurement setup:

#### **Data labels**

There are two sets of data labels. Labels are limited to 32 bits, so there are a total of four data labels.

## To display the captured data

1 In the Workspace window, connect a Listing display to the output of the analyzer.

See the Agilent 16700-series logic analysis system on-line help for information on using the Listing display.

## To display symbols

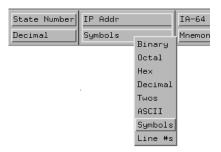

• In the Listing window, select the label base and select Symbols.

You can display a label in symbolic form, if you have defined symbols for that label. Any symbols that have been defined will be displayed in place of the captured values.

For example, if your compiler or assembler outputs a symbol file, you can display IP addresses in terms of the modules and functions in your source code.

See also "Loading Symbol Information" on page 68 and "Loading Configuration Files" on page 60.

# **Displaying Signals as Waveforms**

## To display timing information

To capture these waveforms:

- 1 Load the Timing configuration file.

- **2** In the Workspace window, connect a Waveform tool to the output of the logic analyer tool, as shown on page 81.

You can also use the Waveform display in the state analysis mode to display state timing diagrams.

# **Using Dynamic Data Inversion**

To reduce noise on the data bus, the processor selectively inverts groups of 16 bits. An inversion status bit is associated with each group of 16 bits to indicate whether that group was inverted.

Manually interpreting this data can be cumbersome. As a convenience, the analysis probe un-inverts the inverted data *before sending it to the logic analyzer*, so all data appears logically true. This is called dynamic data inversion.

#### To use dynamic data inversion on the data bus

Dynamic data inversion is enabled by default.

- 1 Open the Probe Control Tool.

- **2** Select the Data Modes tab.

- 3 Select Dynamic Data Inversion.

- **4** Run the measurement.

The advantage of dynamic data inversion is that *all* data will be displayed in its logically true form. The disadvantages of dynamic data inversion are that you will see apparent parity errors (parity calculations include the inversion bits) and that the inversion bits will all appear as 0, regardless of their actual value on the bus.

#### To disable dynamic data inversion

- 1 Open the Probe Control Tool.

- **2** Select the Data Modes tab.

- **3** Unselect Dynamic Data Inversion.

Disable dynamic data inversion if you want to see the data signals as they physically appear on the bus, or if you are using software to post-process the listing, and the software uses the inversion bits.

# **Using Other Tools to Process and Display Your Data**

#### **Useful tools**

Some tools in your logic analysis system which are useful for analysis of IA-32 processors include:

#### **Chart Tool**

For displaying x-y plots of various data values.

#### **Compare Tool**

For comparing a "golden trace" from a known-good target system to a trace from another target system.

#### **Distribution Tool**

For displaying an overview of activity in a bar-graph form.

#### **Pattern Filter**

For excluding selected data from a data stream before you view it or store it.

#### **System Performance Analyzer**

(Licensed separately.) For displaying the distribution of bus events in time, for visually identifying patterns of activity, and for identifying operations which consume significant system resources.

#### **Tool Development Kit**

(Licensed separately.) For writing programs to postprocess data in any way you like.

7 Displaying Captured States

# **Troubleshooting the Analysis Probe**

This chapter explains how to solve problems you could encounter when you use the analysis probe.

If you encounter difficulties while making measurements, use this chapter to guide you through some possible solutions. Each heading lists a problem you may encounter, along with some possible solutions.

The information in this chapter is presented in the following sections:

- · Logic analyzer problems

- · Analysis probe problems

- Inverse assembler problems

- Intermodule measurement problems

- Messages

If you still have difficulty using the analyzer after trying the suggestions in this chapter, please contact your local Agilent Technologies service center.

CAUTION

When you are working with the analyzer, be sure to power down both the analyzer and the target system before disconnecting or connecting cables, the interposer, or the analysis probe. Otherwise, you may damage circuitry in the analyzer, analysis probe, or target system.

# **Logic Analyzer Problems**

This section lists general problems that you might encounter while using the logic analyzer.

#### Intermittent data errors

Intermittent data errors are usually caused by incorrect sampling positions. To set the sampling positions:

- ✓ Deskew the analyzer. See "Deskewing the logic analyzer" on page 62, or

- ✓ If you have saved eye finder data after deskewing the analyzer, and the setup hasn't changed, load the eye finder data file. See "To load Eye Finder data" on page 67.

This problem is can also be caused by poor connections, incorrect signal levels, or marginal timing.

- Remove and reseat all cables and probes, ensuring that there are no bent pins on the analysis probe or poor probe connections.

- ✓ Check that the analysis probe cables and logic analyzer cables have not been physically damaged or kinked.

- ✓ Use an oscilloscope to check the signal integrity of the data lines.

Clock signals for the state analyzer must meet particular pulse shape and timing requirements. Data inputs for the analyzer must meet pulse shape and setup and hold time requirements.

See *Capacitive Loading* in this chapter for information on other sources of intermittent data errors.

## **Unwanted triggers**

The processor fetches from data memory during cache line fills. The "false" trigger may be part of a cache line fill from an instruction in the same cache line.

## Trigger not seen

Only one address of the cache line fill is placed on the address bus. The other addresses are implied. Use "don't care" terms in the trigger to capture any of the cache line addresses.

### No activity on activity indicators

- Check for loose cables, board connections, and analysis probe connections.

- ✓ Check for bent or damaged pins on the analysis probe.

#### No trace list display

If there is no trace list display, it may be that your trigger specification is not correct for the data you want to capture, or that the trace memory is only partially filled.

- ✓ Check your trigger sequencer specification to ensure that it will capture the events of interest.

- ✓ Try stopping the analyzer; if the trace list is partially filled, this should display the contents of trace memory.

# **Analysis Probe Problems**

This section lists problems that you might encounter when using an analysis probe. If the solutions suggested here do not correct the problem, you may have a damaged analysis probe. Contact your local Agilent Technologies Sales Office if you need further assistance.

## Target system will not boot up

If the target system will not boot up after connecting the analysis probe, the microprocessor (if socketed) or the analysis probe may not be installed properly, or they may not be making electrical contact.

✓ Verify the values of the termination resistors on the target system.

Download the latest processor data sheet and verify that the values of the termination resistors meet the specifications.

- ✓ Ensure that you are following the correct power-on sequence for the analysis probe and target system.

- **1** Power up the analyzer and analysis probe.

- **2** Power up the target system.

If you power up the target system before you power up the analysis probe, interface circuitry in the analysis probe may latch up and prevent proper target system operation.

- ✓ Verify that the microprocessor and the interposer are securely inserted into their respective sockets.

- ✓ Verify that the logic analyzer cables are in the proper sockets of the analysis probe and are firmly inserted.

- Remove any extra sockets (pin protectors) which may have been added.

#### Erratic trace measurements

- ✓ Do a full reset of the target system before beginning the measurement.

- ✓ Ensure that your target system meets the timing requirements of the processor with the analysis probe installed.

See *Capacitive loading* in this chapter. While analysis probe loading is slight, pin protectors, extenders, and adapters may increase it to unacceptable levels. If the target system design has close timing margins, such loading may cause incorrect processor functioning and give erratic trace results.

✓ Ensure that you have sufficient cooling for the microprocessor.

Ensure that you have ambient temperature conditions and airflow that meet or exceed the requirements of the microprocessor manufacturer.

## **Capacitive loading**

Excessive capacitive loading can degrade signals, resulting in incorrect capture by the analysis probe, or system lockup in the microprocessor. All analysis probe add additional capacitive loading, as can custom probe fixtures you design for your application.

Careful layout of your target system can minimize loading problems and result in better margins for your design.

Remove as many pin protectors, extenders, and adapters as possible.

#### Data bus is missing

If you do not see any activity on the data bus, it is possible that one or more strobe signals are missing. The strobes may be viewed with the Timing mode configuration. Data is presented in 16-bit slices with the \_1 phase being the P strobe, and the \_2 phase being the N strobe. See page 101 for more information on how the strobes relate to the data phases.

## Analysis probe shuts down

If the analysis probe shuts down after 15-30 minutes of operation, then begins running again, it may be experiencing a thermal shutdown.

- ✓ Check that there is at least 5 cm (2 inches) of space in front of all ventilation holes. See "Bench Space for the Analysis Probe" on page 23.

- ✓ Check that nearby equipment is not heating the analysis probe beyond its recommended temperature range. See "Environmental Characteristics (Operating)" on page 100.

- ✓ If the analysis probe still shuts down, or if you do not hear fans running inside the analysis probe, contact Agilent Technologies.

### **Intermodule Measurement Problems**

Some problems occur only when you are trying to make a measurement involving multiple modules.

#### An event wasn't captured by one of the modules

If you are trying to capture an event that occurs very shortly after the event that arms one of the measurement modules, it may be missed due to internal analyzer delays. For example, suppose you set an oscilloscope module to trigger upon receiving a trigger signal from the logic analyzer because you are trying to capture a pulse that occurs right after the analyzer's trigger state. If the pulse occurs too soon after the analyzer's trigger state, the oscilloscope will miss the pulse.

✓ Adjust the skew in the Intermodule menu.

You may be able to specify a skew value that enables the event to be captured.

✓ Change the trigger specification for modules upstream of the one with the problem.

If you are using a logic analyzer to trigger an oscilloscope module, try specifying a trigger state one state before the one you are using. This may be more difficult than working with the skew because the prior state may occur more often and not always be related to the event you are trying to capture with the oscilloscope.

# **Analysis Probe Messages**

This section lists some of the messages that the analyzer displays when it encounters a problem.

#### "Measurement Initialization Error"

This error occurs when the cables between the logic analyzer cards are installed incorrectly.

Ensure that your cable connections match the silk screening on the card, and that they are fully seated in the connectors. Then, repeat the measurement.

See also the Agilent Logic Analysis Systems Installation Guide.

# "No Configuration File Loaded"

This is usually caused by trying to load a configuration file for one type of module/system into a different type of module/system.

✓ Verify that the appropriate module has been selected from the Load {module} from File {filename} in the disk operation menu. Selecting Load {All} will cause incorrect operation when loading most analysis probe configuration files.

Chapter, "," beginning on page 59, describes how to load configuration files.

## "Selected File is Incompatible"

This occurs when you try to load a configuration file for the wrong module. Ensure that you are loading the appropriate configuration file for your logic analyzer.

### "Slow or Missing Clock"

✓ This error message might occur if the logic analyzer cards are not firmly seated in the logic analysis system frame. Ensure that the cards are firmly seated.

- ✓ This error might occur if the target system is not running properly. Ensure that the target system is on and operating properly.

- ✓ If the error message persists, check that the logic analyzer pods are connected to the proper connectors on the analysis probe.

# "Waiting for Trigger"

If a trigger pattern is specified, this message indicates that the specified trigger pattern has not occurred. Verify that the triggering pattern is correctly set.

✓ When analyzing microprocessors that fetch only from word-aligned addresses, ensure that the trigger condition is set to look for an opcode fetch at an address corresponding to a word boundary. **8 Troubleshooting the Analysis Probe**

# Analysis probe—operating characteristics

Table 2

Operating Characteristics

The following operating characteristics are not specifications,

| Operating Character            | istics                                                                                                                             |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor<br>Supported    | Intel® Pentium® 4 Processor in the 478-Pin Package                                                                                 |

| Socket Supported               | Lever-actuated socket with desktop retention mechanism.                                                                            |

| Clock Frequency                | 200 MHz maximum (BCLK)                                                                                                             |

| Logic Analyzers<br>Supported   | Agilent 16753/4/5/6A logic analyzers in an Agilent 16700-series logic analysis system. (See page 53 for supported configurations.) |

| Analysis Probe<br>Cable Length | Approximately 4 feet                                                                                                               |

Table 3

Inputs and Outputs

| Inputs and Outputs                    |                                                                                                           |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------|

| To interposer                         | 478-pin Intel Pentium 4 processorIntel® Pentium® 4 Processor in the 478-Pin Package                       |

| Between interposer and analysis probe | The Agilent E8046A interposer must be connected only to the cables from an Agilent E8045A analysis probe. |

| From analysis probe                   | High-density connectors for an Agilent 16700-series logic analysis system.                                |

Table 4

Electrical Characteristics

#### **Electrical Characteristics**

**Power** 115/230 Vac +/- 20%, 48-66Hz, 350W power supply is built into the

**Requirements** analysis probe. Line selection is autoranging.

CAT II (Line voltage in appliance and to wall outlet)

Pollution degree 2

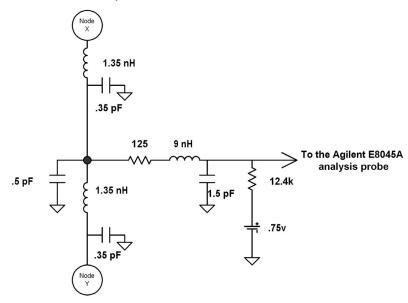

Signal Line Loading GTL+ signals

#### To the Intel processor

To the target motherboard

#### Table 5 Environmental Characteristics (Operating)

#### **Environmental Characteristics (Operating)**

**Temperature**  $20^{\circ} \text{ to} + 30^{\circ} \text{ C } (+68^{\circ} \text{ to} +86^{\circ} \text{ F})$

Altitude 4,600 m (15,000 ft)

**Humidity** Up to 50% noncondensing. Avoid sudden, extreme temperature

changes which could cause condensation on the circuit board.

For indoor use only.

# Signal-to-connector mapping

The following table defines the logic analyzer bit assignments.

#### Key

Signal

Name of the signal coming from the analysis probe into the logic analysis system.

Phase

Due to the source synchrounous nature of the bus, data captured by the logic analyzer in four chunks of 64-bit data. In a four-chunk data transfer, the analysis probe maps the four phases to two separate sets of logic analyzer pins.

| Phase | BCLK | Strobe | Edge             | Mapped to |

|-------|------|--------|------------------|-----------|

| 1     | 0    | P[3:0] | 1st falling edge | LA Card A |

| 2     | 0    | N[3:0] | 1st falling edge | LA Card B |

| 3     | 1    | P[3:0] | 2nd falling edge | LA Card A |

| 4     | 1    | N[3:0] | 2nd falling edge | LA Card B |

For address signals, each of the two phases is mapped to a separate set of logic analyzer pins:.

| Phase | Address strobe | Mapped to |

|-------|----------------|-----------|

| 1     | falling edge   | LA Card D |

| 2     | rising edge    | LA Card E |

Pod-Bit

The logic analyzer pod containing the signal and the bit number of the particular pin on the pod. For some signals, the signal mappings are different in state and timing modes.

Label

Name of the signal coming from the analysis probe into the logic analysis system, as displayed in the Format window or in a Listing window. Upper-case signal names generally correspond to signals from the processor. Lower-case signal names are generally signals generated by the analysis probe to allow the inverse assembler to properly decode bus activity.

# Data signals

| Signal | Phase | Pod-Bit<br>(State) | Pod-Bit<br>(Timing) | Label    | Description                  |

|--------|-------|--------------------|---------------------|----------|------------------------------|

| DBI3#  | 1,3   | A4-16              | A4-8                | DBI1_4#  | A4-16 = Clock M of LA card A |

| D63#   | 1,3   | A4-15              | A4-11               | D63-32_1 |                              |

| D62#   | 1,3   | A4-14              | A4-12               | D63-32_1 |                              |

| D61#   | 1,3   | A4-13              | A4-13               | D63-32_1 |                              |

| D60#   | 1,3   | A4-12              | A4-14               | D63-32_1 |                              |

| D59#   | 1,3   | A4-11              | A4-15               | D63-32_1 |                              |

| D58#   | 1,3   | A4-10              | A4-6                | D63-32_1 |                              |

| D57#   | 1,3   | A4-9               | A4-7                | D63-32_1 |                              |

| D56#   | 1,3   | A4-8               | A4-16               | D63-32_1 |                              |

| D55#   | 1,3   | A4-7               | A4-9                | D63-32_1 |                              |

| D54#   | 1,3   | A4-6               | A4-10               | D63-32_1 |                              |

| D53#   | 1,3   | A4-5               | A4-0                | D63-32_1 |                              |

| D52#   | 1,3   | A4-4               | A4-1                | D63-32_1 |                              |

| D51#   | 1,3   | A4-3               | A4-2                | D63-32_1 |                              |

| D50#   | 1,3   | A4-2               | A4-3                | D63-32_1 |                              |

| D49#   | 1,3   | A4-1               | A4-4                | D63-32_1 |                              |

| D48#   | 1,3   | A4-0               | A4-5                | D63-32_1 |                              |

| DBI2#  | 1,3   | A3-16              | A3-16               | DBI1_3#  | A3-16 = Clock L of LA card A |

| D47#   | 1,3   | A3-15              | A3-15               | D63-32_1 |                              |

| D46#   | 1,3   | A3-14              | A3-14               | D63-32_1 |                              |

| D45#   | 1,3   | A3-13              | A3-13               | D63-32_1 |                              |

| D44#   | 1,3   | A3-12              | A3-12               | D63-32_1 |                              |

| D43#   | 1,3   | A3-11              | A3-11               | D63-32_1 |                              |

| D42#   | 1,3   | A3-10              | A3-10               | D63-32_1 |                              |

| D41#   | 1,3   | A3-9               | A3-9                | D63-32_1 |                              |

| D40#   | 1,3   | A3-8               | A3-8                | D63-32_1 |                              |

| D39#   | 1,3   | A3-7               | A3-7                | D63-32_1 |                              |

| D38#   | 1,3   | A3-6               | A3-6                | D63-32_1 |                              |

| D37#   | 1,3   | A3-5               | A3-5                | D63-32_1 |                              |

| D36#   | 1,3   | A3-4               | A3-4                | D63-32_1 |                              |

| D35#   | 1,3   | A3-3               | A3-3                | D63-32_1 |                              |

| D34#   | 1,3   | A3-2               | A3-2                | D63-32_1 |                              |

| D33#   | 1,3   | A3-1               | A3-1                | D63-32_1 |                              |

| D32#   | 1,3   | A3-0               | A3-0                | D63-32_1 |                              |

| Signal | Phase | Pod-Bit<br>(State) | Pod-Bit<br>(Timing) | Label    | Description                  |

|--------|-------|--------------------|---------------------|----------|------------------------------|

| DBI1#  | 1,3   | A2-16              | A2-16               | DBI1_2#  | A2-16 = Clock K of LA card A |